THE 8051 Microcontroller or Trainer kit

INTRODUCTION

This section begins with a discussion of the role and importance of Microcontroller in everyday life. Microcontrollers are not well known to the general public, or too many in the technical community, as are the glamorous microprocessor. However we are very well aware that “something” is responsible for all of the smart VCRs, clock radios, video games, Telephones, TVs, automobiles, Mobile phones, camcorder, security systems, instrumentation, printers and a myriad of other articles that are intelligent and “programmable”. These all things are due to a smart “Microcontroller”. Microcontrollers are widely used devices in embedded system. An embedded system product using Microcontroller has one and only one task. In such systems there is only one application software that is typically burned into ROM. One Such system is our 89c51 Microcontroller based Trainer kit in which controller is its heart. For our trainer Kit, we have chosen 89c51 microcontroller which is an 8-bit microcontroller from the family of 8051 controllers.

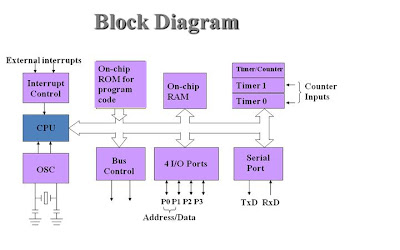

2.2 OVERVIEW OF 89c51 MICROCONTROLLER

89c51 is introduced by Intel corporation is an 8-bit microcontroller. This microcontroller has 128 bytes of RAM, 4K of on-chip ROM, two timers, one serial port, and four ports of 8-bits each all on a single chip. 89c51 is basically Flash ROM version of 8051 family. 89c51 is basically a 40 pin Dual-in-package. Block Diagram of 89c51 is as shown in figure, which shows the microcontroller Hardware. The main features of 89c51 Hardware can be labeled as below:

1. It has 8-bit CPU with registers A (the accumulator) and B.

2. Sixteen-bit program counter (PC) and data pointer (DPTR).

3. Eight-bit program status word (PSW).

4. Eight-bit stack pointer (SP).

5. Internal ROM of 0 to 4K.

6. Internal RAM of 128 bytes.

7. 32 I/0 pins arranged as four 8-bit ports: P0-P3

8. Two 16-bit Timer/Counters: T0 and T1

9. Full duplex serial data receiver/transmitter: SBUF

10. Control registers: TCON, TMOD, SCON, PCON, IP, and IE.

11. Two external and three internal interrupt sources.

12. Oscillator and Clock circuits.

A pin out of the 89c51 packaged in a 40 pin DIP is as shown in figure:

Pin descriptions:

1. VSS (pin-20)

Ground= 0 V reference.

2. VCC (pin-40)

This is the power supply voltage for normal, idle and power-down modes.

3. P.0-P0.7 (pin-39 to pin 32 i.e., port 0)

Port 0 is an open-drain, bidirectional I/O port. Pins of Port 0 on which there is a high logic will float and can be used as a high impedance inputs. Port 0 is also the multiplexed low-order address and data bus during accesses to external program and data memory; In this application it uses strong internal pull-ups for emitting 1’s.

4. P1.0-P1.7 (pin-1 to pin 8 i.e., port 1)

Port 1 is an 8-bit bidirectional I/O port with internal pull-ups. Port 1 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, port 1 pins that are externally pulled low will source current because of the internal pull-ups.

5. P2.0-p2.7 (pin-21 to pin-28 i.e., port 2)

Port 2 is an 8-bit bidirectional I/O port with internal pull-ups. Port 2 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, port 2 pins that are externally being pulled low will source current because of the internal pull-ups. Port 2 emits the high-order address byte during fetches from external program memory and during accesses to external data memory that uses 16-bit addresses (MOVX @DPTR). In this application, it uses strong internal pull-ups when emitting 1s. During accesses to external

Data memory that use 8-bit addresses (MOV @Ri), port 2 emits the contents of the P2 special function register.

6. P3.0-p3.7 (pin-10 to pin-17 i.e., port 3)

Port 3 is an 8-bit bidirectional I/O port with internal pull-ups. Port 3 pins that have 1s written to them are pulled high by the internal pull-ups and can be used as inputs. As inputs, port 3 pins that are externally being pulled low will source current because of the pull-ups. Port 3 also serves the special features of the 89C51, as listed below:

RxD (P3.0): Serial input port.

TxD (P3.1): Serial output port.

INT0 (P3.2): External interrupt.

INT1 (P3.3): External interrupt.

T0 (P3.4): Timer 0 external input.

T1 (P3.5): Timer 1 external input.

WR (P3.6): External data memory write strobe.

RD (P3.7): External data memory read strobe.

7. RESET (pin-9)

A high on this pin for two machine cycles while the oscillator is running resets the device. An internal diffused resistor to VSS permits a power-on reset using only an external capacitor to VCC

8. ALE (pin-30)

Output pulse for latching the low byte of the address during an Access to external memory. In normal operation, ALE is emitted at a constant rate of 1/6 the oscillator frequency, and can be used for external timing or clocking. Note that one ALE pulse is skipped during each access to external data memory. ALE can be disabled by setting SFR auxiliary.0. With this bit set, ALE will be active only during a MOVX instruction.

9. PSEN (pin-29)

The read strobe to external program memory. When executing code from the external program memory, PSEN is activated twice each machine cycle, except that two PSEN activations are skipped during each access to external data memory. PSEN is not activated during fetches from internal program memory.

10. EA/VPP (pin-31)

EA must be externally held low to enable the device to fetch code from external program memory locations 0000H to the maximum internal memory boundary. If EA is held high, the device executes from internal program memory unless the program counter contains an address greater than 0FFFH for 4 k devices, 1FFFH for 8 k devices, 3FFFH for 16 k devices, and 7FFFH for 32 k devices. The value on the EA pin is latched when RST is released and any subsequent changes have no effect. This pin also receives the 5V/12V programming supply voltage (VPP) during FLASH programming.

11. XTAL1 and XTAL2 (pin-18 and pin-19)

Crystal 1: Input to the inverting oscillator amplifier and input to the internal clock generator circuits.

Crystal 2: Output from the inverting oscillator amplifier.

OSCILLATOR CHARACTERISTICS:

XTAL1 and XTAL2 are the input and output, respectively, of an Inverting amplifier. The pins can be configured for use a an On-chip oscillator. To drive the device from an external clock source, XTAL1 should be driven while XTAL2 is left unconnected. There are no requirements on the duty cycle of the external clock signal, because the input to the internal clock circuitry is through a divide-by two flip-flop. However, minimum and maximum high and low times specified in the data sheet must be observed.

RESET:

A reset is accomplished by holding the RST pin high for at least two machine cycles (24 oscillator periods), while the oscillator is running. To insure a good power-on reset, the RST pin must be high long enough to allow the oscillator time to start up (normally a few milliseconds) plus two machine cycles. At power-on, the voltage on VCC and RST must come up at the same time for a proper start-up. Ports 1, 2, and 3 will asynchronously be driven to their reset condition when a voltage above VIH1 (min.) is applied to RST. The value on the EA pin is latched when RST is disserted and has no further effect.

Accumulator:

The A (Accumulator) is the versatile of the two CPU registers and is used for many operations, including addition, subtraction, division, integer multiplication and Boolean bit manipulations. The A register is also used for data transfers between the 8051 and any external memory.

B Register:

The B register is used during multiply and divide operations. For other instructions it can be treated as another scratch pad register.

Program Status Word:

The PSW register contains program status information as detailed in Table below: The PSW consists of math flags, user program flag F0, and the register bank select bits that identify which of the four general register banks is currently in use by the program.

Stack Pointer:

The Stack Pointer register is 8 bits wide. It is incremented before data is stored during PUSH and CALL executions. While the stack may reside anywhere in on-chip RAM, the Stack Pointer is initialized to 07H after a reset. This causes the stack to begin at locations 08H.

Data Pointer:

The Data Pointer (DPTR) consists of a high byte (DPH) and a low byte (DPL). Its intended function is to hold a 16-bit address. It may be manipulated as a 16-bit register or as two independent 8-bit registers.

Serial Data Buffer:

The Serial Buffer is actually two separate registers, a transmit buffer and a receive buffer. When data is moved to SBUF, it goes to the transmit buffer and is held for serial transmission. (Moving

A byte to SBUF is what initiates the transmission.) When data is moved from SBUF, it comes from the receive buffer.

Timer Registers:

Register pairs (TH0, TL0), and (TH1, TL1) are the 16-bit Counting registers for Timer/Counters 0 and 1, respectively.

Control Register:

Special Function Registers IP, IE, TMOD, TCON, SCON, and PCON contain control and status bits for the interrupt system, the Timer/Counters, and the serial port. They are described in later sections.

2.3 TIMERS AND COUNTERS:

Timer 0 and Timer 1:

The “Timer” or “Counter” function is selected by control bits C/T in the Special Function Register TMOD. These two Timer/Counters have four operating modes, which are selected by bit-pairs (M1, M0). In TMOD. Modes 0, 1, and 2 are the same for both Timers/Counters. Mode 3 is different. The four operating modes are described in the following text:

Mode 0:

Timer, which is an 8-bit Counter with a divide-by-32 pre scalar. Figure shows the Mode 0 operation as it applies to Timer 1. In this mode, the Timer register is configured as a 13-bit register. As the count rolls over from all 1s to all 0s, it sets the Timer interrupt flag TF1. The counted input is enabled to the Timer when TR1 = 1 and either GATE = 0 or INT1 = 1. (Setting GATE = 1 allows the Timer to be controlled by Putting either Timer into Mode 0 makes it look like an 8048 external input INT1, to facilitate pulse width measurements). TR1 is a control bit in the Special Function Register TCON (Figure 3). GATE is in TMOD. The 13-bit register consists of all 8 bits of TH1 and the lower 5 bits of TL1. The upper 3 bits of TL1 are indeterminate and should be ignored. Setting the run flag (TR1) does not clear the registers. Mode 0 operation is the same for the Timer 0 as for Timer 1. Substitute TR0, TF0, and INT0 for the corresponding Timer 1 signals in Figure 2. There are two different GATE bits, one for Timer 1 (TMOD.7)

And one for Timer 0 (TMOD.3).

Mode 1: Mode 1 is the same as Mode 0, except that the Timer register is being run with all 16 bits.

Mode 2: Mode 2 configures the Timer register as an 8-bit Counter (TL1) with automatic reload, as shown in Figure 4. Overflow from TL1 not only sets TF1, but also reloads TL1 with the contents of TH1, which is preset by software. The reload leaves TH1 unchanged. Mode 2 operation is the same for Timer/Counter 0.

Mode 3: Timer 1 in Mode 3 simply holds its count. The effect is the same as setting TR1 = 0. Timer 0 in Mode 3 establishes TL0 and TH0 as two separate counters. The logic for Mode 3 on Timer 0 is shown in Figure 5. TL0 uses the Timer 0 control bits: C/T, GATE, TR0, and TF0, as well as the INT0 pin. TH0 is locked into a timer function (counting machine cycles) and takes over the use of TR1 and TF1 from Timer 1. Thus, TH0 now controls the “Timer 1” interrupt. Mode 3 is provided for applications requiring an extra 8-bit timer on the counter. With Timer 0 in Mode 3, an 80C51 can look like it has three Timer/Counters. When Timer 0 is in Mode 3, Timer 1 can be turned on and off by switching it out of and into its own Mode 3, or can still be used by the serial port as a baud rate generator, or in fact, in any application not requiring an interrupt. TCON and TMOD are the two registers used for setting the above modes. The format of these registers are as shown in figure: TMOD is dedicated solely to the timers and can be considered to be two duplicate 4-bit registers, each of which controls the action of one of the timers. TCON has

Control bits and flags for the timers in the upper nibble, and control bits and flags for the external interrupts in the lower nibble. Figure shows the bit assignments for TMOD and TCON.

2.4 CRITERIA FOR CHOOSING 89c51 MICROCONTROLLER

1. The first and foremost criterion in choosing a microcontroller is that it must meet the task at hand efficiently and cost effectively. In our project we have chosen an 8-bit microcontroller which can handle the computing needs of the task most effectively.

2. The highest speed this microcontroller can support is 12MHZ.

3. To fulfill our requirements in terms of space, assembling, we have chosen the 40-pin DIP.

4. To support the memory requirement we have chosen it as it includes 4K ROM and 128byte RAM.

5. As there are 32 I/O pins and 2 timers, it supports our input-output requirement Greatly.

6. We have used the battery power product like an RTC the power consumption is Critical for it.

7. In choosing this controller we have considered the availability of an assembler, debugger, simulator etc.

8. The ready availability in needed quantities both now and in the future. Currently, of the leading 8-bit microcontrollers, the 8051 family has the largest number of diversified suppliers.

Comments